Différence entre les MIP et le bras

Mips vs bras

Un certain nombre de différences entre les MIP et les bras peuvent être identifiées, mais les deux se trouvent dans la même famille d'ensembles d'instructions. D'ailleurs, MIPS et ARM sont deux architectures d'instructions (ISA) qui sont disponibles dans le monde des microprocesseurs. Les ARM et les MIP, sont basés sur un information d'instructions réduite (RISC) et ils sont en type d'enregistrement. Les deux ensembles d'instructions ont une taille d'instruction fixe 32 bits / 64 bits (espace d'adressage) et les deux ensembles d'instructions peuvent être configurés sur Big Endianness ainsi que Little Endianness. Les deux architectures prennent en charge la compatibilité arrière. Les architectures des ARM et des MIP sont utilisées dans les processeurs de téléphones intelligents et de tablettes tels que les iPhones, les tablettes Android et Windows RT, mais pas dans les ordinateurs de flux principal tels que les ordinateurs portables et les serveurs.

Qu'est-ce que le bras?

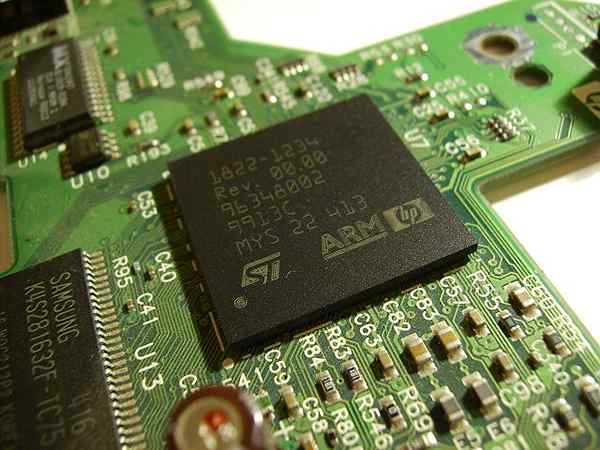

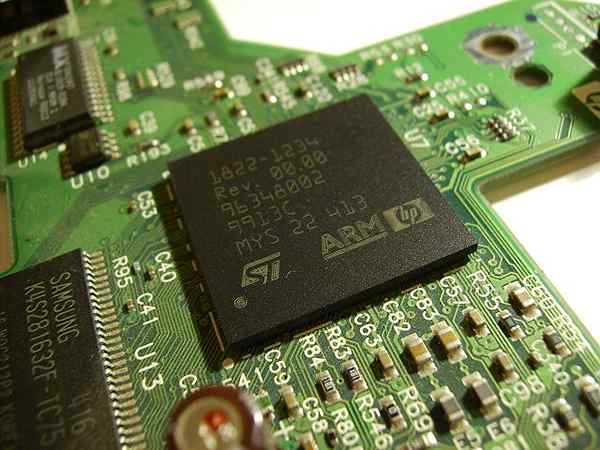

Le concepteur principal de ARM ISA est les titres de bras. L'architecture du bras a été introduite en 1985 et conçue sur la base de RISC. Cet Isa utilise des codes conditionnels dans la branche. Il existe plusieurs architectures ARM telles que des architectures 64/32 bits, des architectures 32 bits (cortex) et des architectures 32 bits (héritage). ARM est l'architecture d'ensemble d'instructions la plus utilisée au monde. L'ensemble d'instructions ARM peut être divisé en six grandes classes d'instructions telles que les instructions de branche, les instructions de traitement des données, les instructions de chargement et de stockage, les instructions de coprocesseur et les instructions générateurs d'exception. Différents types d'instructions de bras peuvent être identifiés à l'aide de l'opcode et des indicateurs conditionnels. Il y a 16 registres à usage général appelé R0 à R15 dans le bras Isa et chacun a une taille de 32 bits. Le registre R13 est appelé Pile Pointer (SP), R14 est appelé Link Register (LR) et R15 est appelé Program Counter (PC). ARM ISA prend en charge de nombreuses opérations arithmétiques telles que l'ajout, la soustraction et la multiplication. Les noyaux de bras ont un bus d'adresse 32 bits, qui fournit un espace d'adressage linéaire plat de 4 Go plat. La mémoire est traitée en octets et peut être accessible sous forme de mots doubles (8 octets), de mots (4 octets) ou de demi-mots (2 octets).

Les architectures de bras sont utilisées dans les téléphones intelligents, les PDA de tablettes et d'autres appareils mobiles. Les puces de bras sont également utilisées dans Raspberry Pi, Beagleboard, Pandaboard et autres ordinateurs monomodes en raison de leur petite consommation d'énergie, de leur bon marché et de leur forme plus petite.

Qu'est-ce que MIPS?

MIPS a été conçu et introduit par MIPS Technologies en 1981. Cet ISA est également basé sur l'architecture d'instructions RISC et possède un système de codage fixe. Les registres de condition sont utilisés pour la ramification et MDMX, les MIPS-3D sont utilisés comme extensions. Il existe trois types d'instructions MIPS et ce sont R, I et J. Chaque instruction commence par un opcode 6 bits. Dans les instructions de type r, il y a trois registres, un champ de montage à décalage et un champ de fonction. Dans les instructions de type I, il y a deux registres et une valeur immédiate 16 bits tandis que les instructions de type j suivent OPCode avec une cible de saut de 26 bits. MIPS a 32 registres entiers afin d'effectuer des opérations arithmétiques. Enregistrement 0 $ contient 0 et l'enregistrement 1 $ est normalement réservé à l'assembleur.

L'architecture MIPS est utilisée pour fabriquer des téléphones intelligents, des ordinateurs de souper, des systèmes intégrés tels que des routeurs, des passerelles résidentielles et des consoles vidéo telles que Sony Playstations.

Quelle est la différence entre les MIP et le bras?

• Les MIP et les bras sont deux architectures d'instructions différentes dans l'ensemble d'instructions de la famille de RISC.

• Bien que les deux ensembles d'instructions aient une taille d'instruction fixe et même, ARM n'a que 16 registres tandis que MIPS a 32 registres.

• ARM a un débit élevé et une grande efficacité que les MIP car les processeurs ARM prennent en charge les bus de données 64 bits entre le noyau et les caches.

• Afin de permettre un changement de contexte efficace, l'architecture MIPS prend en charge la mise en œuvre de plusieurs banques de registres. ARM ne fournit que des registres à des fins générales pour les opérations arithmétiques et toutes les autres fonctions, mais MIPS fournit deux registres distincts pour maintenir les résultats du fonctionnement multiplié.

• MIPS n'a aucune instruction équivalente à l'instruction ARM MOV.

• Les MIPs ajoutent des instructions génèrent normalement une exception sur le débordement, il est donc rarement utilisé que dans le bras.

• Toutes les instructions de traitement des données ARM définissent les codes de condition ALU par défaut, mais MIPS fournit le SLT à titre de comparaison.

Résumé:

Mips vs bras

Dans le monde des microprocesseurs, MIPS et ARM font un excellent service au nom de leurs architectures d'instructions. MIPSIS a mis en œuvre principalement dans des systèmes intégrés. Mais, à l'heure actuelle, le bras est devenu beaucoup plus populaire dans l'industrie que les MIP.

Images gracieuseté:

- Un processeur ARM dans une imprimante Hewlett-Packard PSC-1315 par Socram8888 (CC par 2.0)

- Vue inférieure du paquet de R4700 par Dyl (CC BY-SA 3.0)